|

Home Image Processor --- HIP |

||

| Home

Projects About Me

|

The HIP is a prototype for a home image processing device to interconnect

home video components, much as present "stereo" (audio) systems

interconnect TVs, VCRs, tuners, CD players, and so on.

Another view is that it is a look at some desirable set-top-box (STB)

functionality.

The HIP can analyze, modify, or synthesize video continuously in real time.

It has been used for a variety of human interface, people tracking,

and video analysis projects.

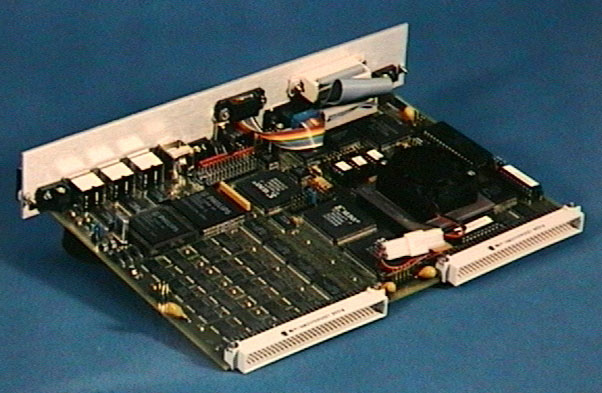

The HIP uses a 42 MHz Motorola 88110 processor, and 16 MB of dynamic RAM, organized as a two-way-interleaved 64 bit system (128 bit total) to provide high peak bandwidth. The memory bandwidth supports its unified memory architecture (UMA) approach, where video and audio are constantly being digitized and stored into memory, modified by the processor, and simultaneously being read out and returned to analog form for display. The system occupies a single VME-format card.

I developed the HIP at AT&T Bell Laboratories in 1992-3.

|